# Switch to 25/100 Gbit/s

by Franck Lefèvre Sales director flefevre@interfaceconcept.com

# Background

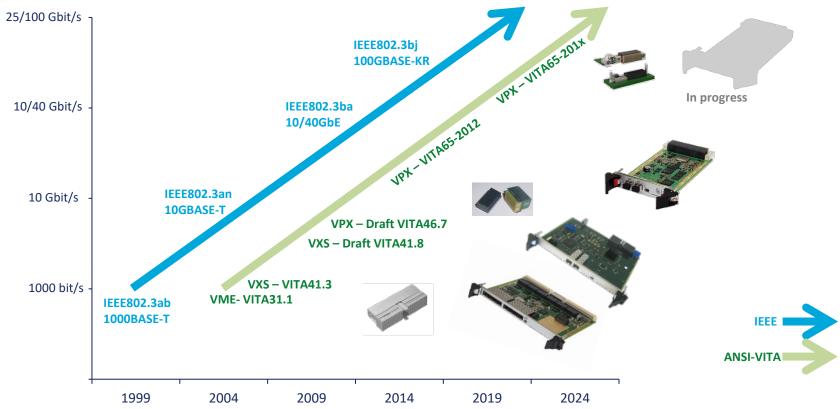

# Technology shift

### 10/40 Gbit/s

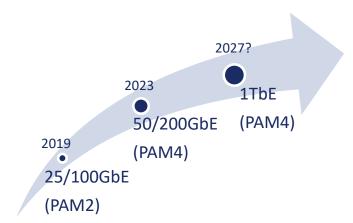

### 25/100 Gbit/s

| Switch technology | SerDes@10Gbit/s                                         | High speed enhanced SerDes                                 |

|-------------------|---------------------------------------------------------|------------------------------------------------------------|

| Protocols         | 10GBASE-KR/40GBASE-KR4                                  | 25GBASE-KR/100GBASE-KR4                                    |

| Signaling speed   | 10.3125 GBd (per lane)                                  | 25.78125 GBd (per lane)                                    |

| Encoding          | 64b/66b block                                           | 256b/257b (PAM2 with NRZ)                                  |

| PCB material      | FR408, MEGTRON 6                                        | MEGTRON 7, Tachyon®-100G                                   |

| Connectors        | RT-2 (R), <i>Light</i> ABLE™                            | RT-3, LightABLE™ LL                                        |

| Ecosystem         | Xeon®-D, QorIQ® T/LS,<br>ARM Cortex-A72, Virtex-6/7etc. | ARM Cortex-A7+, QorlQ LX2xxx,<br>UltraScale+™, Ice Lake-D. |

| Watts             | 4 lanes @ 10G => 1.6 W                                  | 4 lanes @ 25G => 2.8 W                                     |

### Challenges to address

#### Heat Dissipation

Air Flow Thru, and Liquid Flow Thru Cooling

#### New SI Modeling and PCB Materials

Signal Rates now increase from 10Gbit/s to 25Gbit/s New PCB routing methods, mainly for the vias definitions Continuous correction between Simulation and Measurement New measurements tools (VNA) to qualify signals Higher Speed PCB Material, like Megtron 7

#### New connectors

RT3 Connectors and other fiber optic connectors

#### Integration and Test complexity at the system level

VITA68.1 compliance for each part of the system Investment in High-end test equipment

Spirent test center

# Switching to 25/100 Gbit/s is obvious

### Strengths

**W**eaknesses

Ethernet switch is now ubiquitous

25/50/100Gbit/s are standardized

Speeds supported by chips, connectors and material

Time to design/market

Complexity of integration

Cost of development / Cost of technology

Enhanced comms' channels vs processing capabilities

Extra bandwidth to provide more security functions

Increase the product value

Products cost and related industrial risks

The market size is TBD

Incomplete ecosystem (Chipsets, Boards, PCBs etc.)

**O**pportunities

**T**hreats

## Summary

- Ethernet is the preferred network interconnect technology

- IEEE Core standards allow early access to support PHY, and Matrix Chips

- Market will depend on Sensors and Systems needs

- Chip Performance requires high module interface speeds driven by new FPGAs, Processors and GPGPUs

- New Cooling standards will be required

- Transition to Terabit Ethernet will be again more expensive

### INTERFACE CONCEPT

Thank you for your attention!

www.interfaceconcept.com